Como el proveedor de semiconductores más vendido del mundo, Intel no solo desarrolla chips, sino que también investiga sus tecnologías centrales. La División de Investigación de Componentes de Intel presenta ocho proyectos en el Encuentro Internacional de Dispositivos Electrónicos (IEDM 2021), que van desde transistores CMOS en miniatura hasta procesos de apilamiento 3D y chips para computadoras cuánticas.

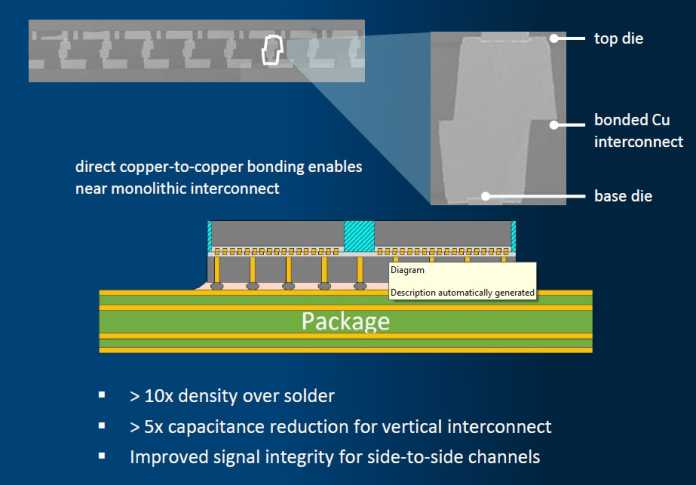

En Foverros Direct, alias HBI, Intel hace contacto directo con dos moldes de silicona apilados con pequeñas puntas de cobre.

(Foto: Intel)

Interconexión de enlace híbrido (HBI)

Si bien las nuevas combinaciones de transistores como FET complementario (CFET) y puerta 3D en todo (GAA) solo aparecerán en la producción en serie después de 2025 y los elementos de lógica de giro magnetoeléctrico (MESO) incluso más tarde, el “Foveros Direct” de Intel también conocido como The Hybrid Bonding Interconnect (HBI) ) El nombre está prácticamente frente a la puerta. Según Intel, se puede utilizar a partir de la tecnología de producción de 7 nm “Intel 4” o “Intel 3”.

En HBI, Intel empaqueta dos chips de silicio directamente uno encima del otro, con poco cobre en contacto entre sí. Según Intel, esto significa que es posible aumentar significativamente la cantidad de contactos por milímetro cuadrado en comparación con los procesos de apilado de matrices anteriores que utilizaban pequeñas bolas de soldadura (rebabas). AMD ya ha anunciado que TSMC producirá “3D V-Cache” para sus próximos procesadores Epyc y Ryzen utilizando un proceso similar. Xperi también licencia uno a través de su división Tessera “Interconexión de enlace directo” (DBI) o ZiBond.

GAA-FET-Stapel

No solo Intel, sino también Samsung y TSMC reemplazarán el transistor de efecto de campo (FET) con un electrodo de compuerta en forma de aleta (FinFET) que se ha construido durante varios años con las próximas series de producción. En su lugar, se utilizan FET de nanocintas, nanohojas y puerta universal (GAA). La versión de Intel se llama RibbonFET y debería venir después de 2023 con la tecnología de producción “Intel 20A”.

En el proceso de fabricación de semiconductores de óxido de metal complementario (CMOS) de décadas de antigüedad, se combina un MOSFET de canal ny canal p (NMOS / PMOS), generalmente en tándem.

Sin embargo, para ahorrar espacio, es decir, colocar más transistores en la superficie del chip, Intel planea apilarlos en el futuro. Para el “Apilamiento 3D de Nanoribbon”, Intel Component Research está experimentando con dos enfoques: construir dos capas funcionales una por una (secuencialmente) con una capa de óxido aislante (silicio) entre ellas o una estructura “autoalineable” directamente una encima de la otra. . Las estructuras similares también se denominan FET complementarias (CFET).

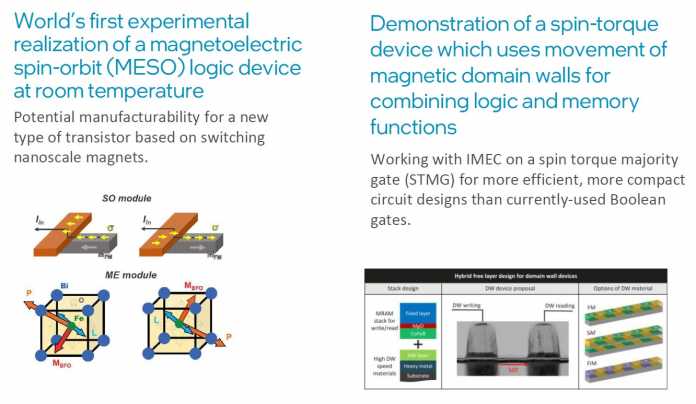

La lógica MESO (izquierda) puede eventualmente reemplazar a CMOS; STMG utiliza límites de campo magnético en movimiento.

(Foto: Intel)

MESO. Lógica

Cuando no todos los paquetes CMOS ayudan a que la Ley de Moore continúe, es hora de reemplazar la CMOS. Es por eso que se han realizado conferencias sobre nanotubos de carbono (CNT) en conferencias de semiconductores durante años.

Intel informa ahora sobre los primeros experimentos exitosos con elementos lógicos MESO a temperatura ambiente, pero escribe que “se pueden producir en serie”.

Otra idea son los componentes de torsión que utilizan transmisión de límite de campo magnético (paredes de dominio, DW); Intel está colaborando con European IMEC en la investigación de Spin Torque Majority Gate (STMG), que es una combinación del componente lógico y de memoria.

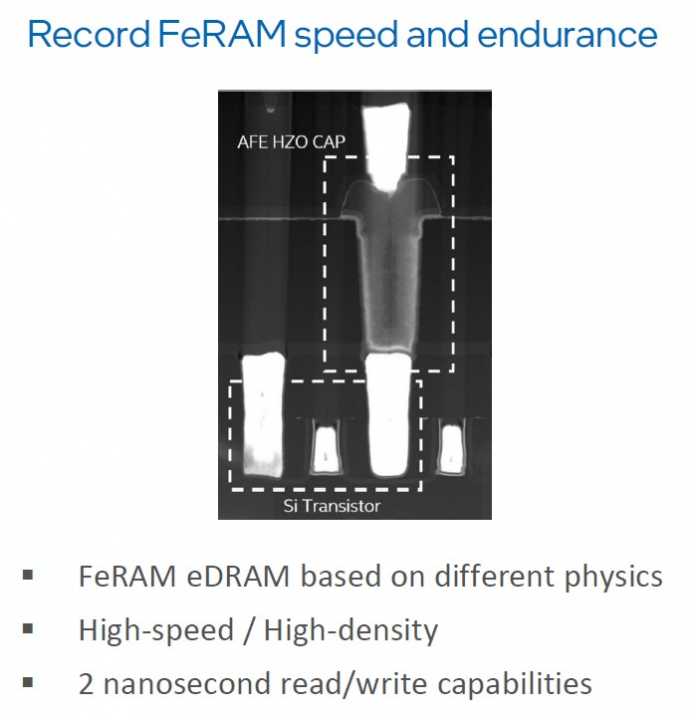

Intel Viram

Celda de viram con óxido de hafnio

(Foto: Intel)

Una celda de memoria FeRAM que utiliza un condensador antielectrolítico a base de hafnio en lugar de una arquitectura de condensador convencional podría estar más cerca del uso práctico. Según Intel, esto significa que midió tiempos de latencia muy cortos de 2 nanosegundos y una resistencia de escritura muy alta (resistencia) en el rango de mil millones de ciclos. Sin embargo, otros fabricantes también están trabajando en FeRAM, incluidos FMC en Dresde.

Otras innovaciones que Intel presentará en IEDM 2021 incluyen la integración de transistores de conmutación de nitruro de galio (GaN) de alto rendimiento en chips CMOS de 300 mm. Esto significa que los transformadores de voltaje eficientes se pueden integrar directamente en los procesadores futuros.

Además, Intel está experimentando con calcogenuros de metales de transición (monocapas TMD) como el disulfuro de molibdeno (MoS).2) como sustituto del silicio en algunos lugares de los semiconductores. Esto puede hacer que algunas estructuras sean más pequeñas.

(una línea)

More Stories

Lanzamiento de un nuevo juego de cartas coleccionables para Android e iOS

En retrospectiva en Apple: ya no hay MacBooks con 8GB de RAM

En lugar de la descripción general de audio NotebookLM de Google: Meta trae NotebookLlama