anuncio

Los fabricantes de chips como TSMC, Intel y Samsung, así como grupos de investigación de IBM, el IMEC de Bélgica y la Universidad Yang Ming Chiao Tung de Taiwán, están desarrollando nuevos conceptos de transistores. Se utilizarán en futuros procesos de fabricación de componentes semiconductores que produzcan estructuras de menos de 2 nm. Entre otras cosas, quieren utilizar estructuras cristalinas ultrafinas que formen capas de sólo unos pocos átomos de espesor y que tengan propiedades eléctricas especiales.

En los últimos años, en conferencias especializadas como la Reunión Internacional de Dispositivos Electrónicos (IEEE IEDM), los investigadores han presentado repetidamente estudios sobre materiales “2D” hechos de dicalcogenuros de metales de transición (TMD), como el disulfuro de molibdeno (MoS).2) y seleniuro de tungsteno (WSe2).

Intel y TSMC planean utilizar las capas como canales conductores para los próximos transistores de efecto de campo (FET). Para ello se necesitan diferentes materiales porque MoS2 Particularmente adecuado para FET de canal n, mientras que WSe2 Mejor para FET de canal p. Sin embargo, los FETS de canal n y p (CMOS significa semiconductor libre de óxido metálico), que funcionan de forma complementaria, deben fabricarse de tal manera que sus propiedades eléctricas coincidan entre sí. También existe el problema de que las capas finas deben poder fabricarse con suficiente resistencia en grandes series para poder sobrevivir de forma fiable a los siguientes pasos de producción.

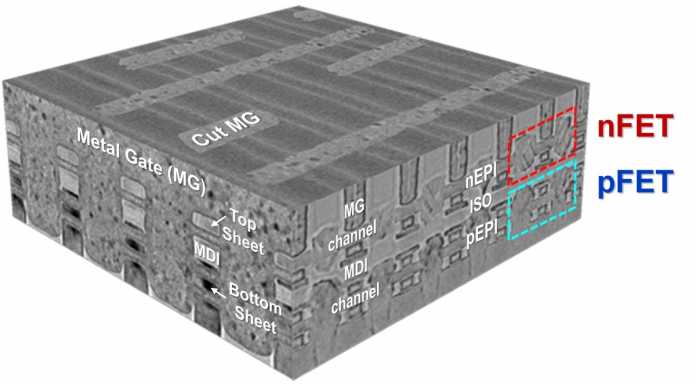

Sección de un chip experimental de TSMC con CFET.

(Imagen: TSMC/IEDM)

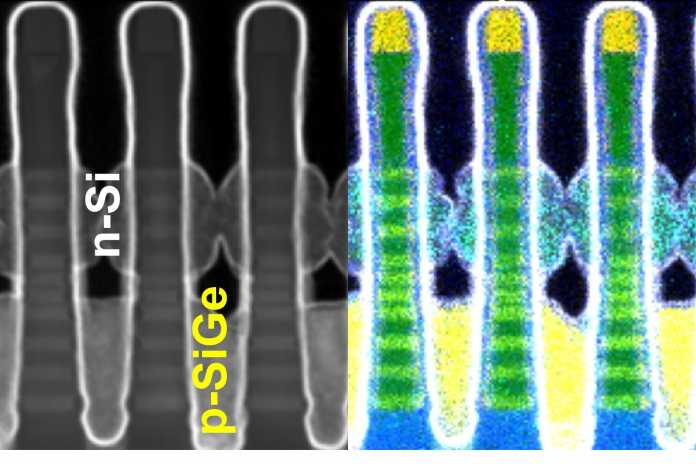

TSMC proporciona buenos resultados de medición para n- y p-FET con canales hechos de MoS en IEDM2-El WSe2-Capas delgadas. fue MoS2-El canal n-FET se inserta entre las capas de óxido de hafnio (HfOx) y nitruro de titanio (TiN). TSMC también demostró una estructura de capas apiladas de n-FET con MoS2-Nano papeles.

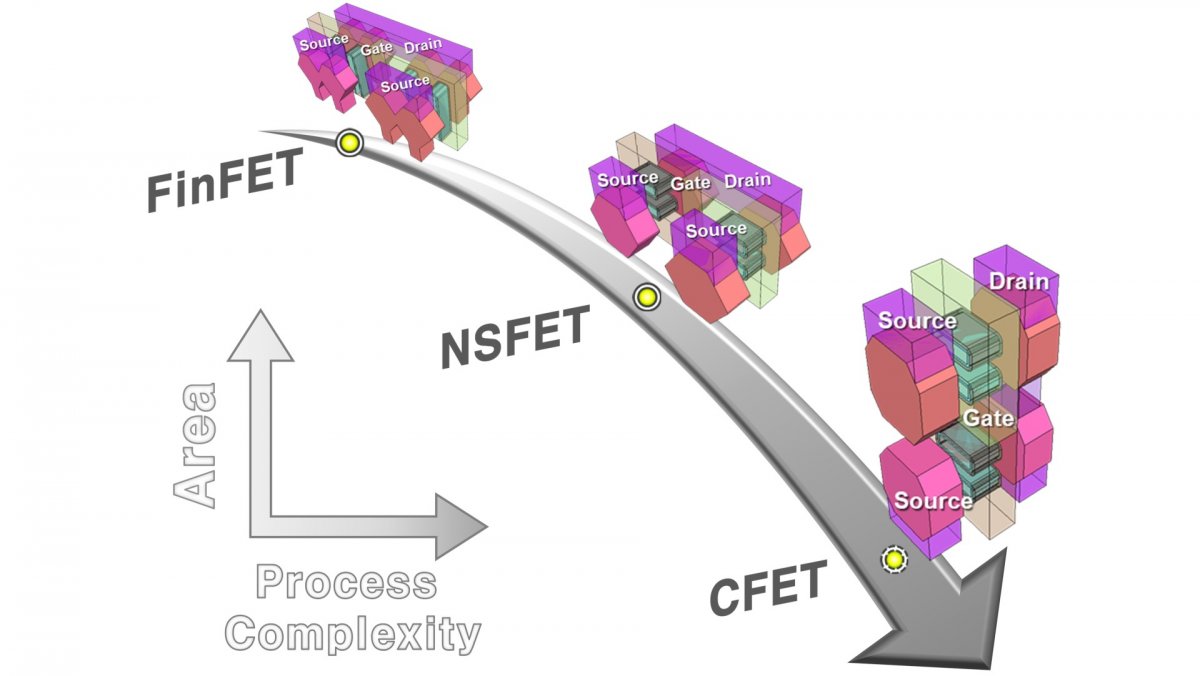

Pares FET complementarios

TSMC e Intel están trabajando en pares de transistores apilados que ocupan una pequeña huella de silicio y actúan como inversores CMOS con un electrodo de puerta común: los FET de flotación libre (CFET). Intel introdujo esta estructura CFET con tres “nano-cintas” n-FET y p-FET cada una, que en realidad están diseñadas para la producción en chip con una fuente de alimentación de back-end a través del material base de silicio. Intel llama a esta tecnología interna de entrega de energía trasera (BPD) “PowerVia” porque los contactos de la fuente de alimentación pasan a través del chip delgado como puertos.

Micrografía de una sección a través de CFET Intel con tres finas capas TMD por transistor.

(Imagen: Intel/IEDM)

IMEC presenta resultados de investigación sobre entrega de energía back-end en IEDM. Por consiguiente, el procesamiento del reverso de la lámina no tiene ningún efecto destructivo sobre las capas superiores. Tal y como estaba previsto, el BPD permite separar las líneas más gruesas de la fuente de alimentación de las señales de datos en el otro lado del chip, encima de los transistores.

Investigadores de la Universidad Yangming Chiao Tung, en colaboración con TSMC, han desarrollado un método para generar múltiples MoS2-Apilar las capas individuales una encima de otra y conectarlas con una unión metálica en forma de C. Esto da como resultado una baja resistencia de contacto del FET de puerta general (GAA) con las nanohojas (nanohojas FET, NSFET) creadas de esta manera.

Escuche también:

(SEO)

“Analista exasperantemente humilde. Experto en tocino. Orgulloso especialista en alimentos. Lector certificado. Escritor ávido. Defensor de los zombis. Solucionador de problemas incurables”.

More Stories

Informe de mercado: Las preocupaciones sobre los tipos de interés y las elecciones estadounidenses pesan sobre el DAX

90 casos de enfermedad en 13 estados: bacterias coliformes encontradas en McDonald’s

Gran pedido: Riyadh Air añade 60 aviones Airbus A321neo a su flota